Salvatore Levantino

Politecnico di Milano

Salvatore Levantino

Politecnico di Milano

Research

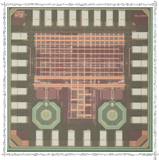

Main field of research is the design of mixed-signal and RF circuit and system, with particular emphasis on solid-state implementations. Contributions have been provided in the study of new architectures for the CMOS integration of radio terminals and in the analysis and design of critical building blocks such as low-phase-noise oscillators and frequency synthesizers. Currently, the research is focusing on the 5G communication standard. Taking advantage of the digitally-intensive design enabled by ultra-scaled CMOS processes, new methodologies and design strategies have been conceived which aim at highly-efficient wireless transmitters, robust to process and environmental variability. The most recent result has been the demonstration of a wideband phase modulator based on a all-digital fractional-N frequency synthesizer in 28nm CMOS, presented at the 2020 International Solid-State Circuits Conference (ISSCC) in San Francisco. The 14GHz circuit features low phase noise (integrated jitter is <60fs) and spurs (<-60dBc) although the power-hungry time-to-digital converter (TDC) is substituted by a simple early-late detector. This realization of fractional-N synthesizer has reached the best power-jitter trade-off so far reported. The synthesizer performance is independent of the variability of analog parameters, thanks to the adoption of digitally-intensive calibrations operating in background.

-A 12.5GHz Fractional-N Type-I Sampling PLL Achieving 58fs Integrated Jitter, ISSCC, Feb. 2020

-A 66fsrmsJitter 12.8-to-15.2GHz Fractional-N Bang-Bang PLL with Digital Frequency-Error Recovery for Fast Locking, ISSCC, Feb. 2020

-A 20Mb/s phase modulator based on a 3.6GHz digital PLL with −36dB EVM at 5mW power, ISSCC, Feb. 2012

-A 2.9-to-4.0GHz Fractional-N Digital PLL with Bang-Bang Phase Detector and 560 fsrms Integrated Jitter at 4.5 mW Power, JSSC, Dec. 2011

-A Wideband 3.6 GHz Digital ΔΣ Fractional-N PLL With Phase Interpolation Divider and Digital Spur Cancellation, JSSC, March 2011

-Suppression of flicker noise upconversion in a 65 nm CMOS VCO in the 3.0-to-3.6 GHz band, ISSCC, Feb. 2010

-Folding of Phase Noise Spectra in Charge-Pump Phase-Locked Loops Induced by Frequency Division, TCAS-II, Sep. 2010

CMOS, wireless, 5G communications, cognitive radio, adaptive filtering, all-digital PLLs, frequency synthesis, low-noise oscillators, phase noise, jitter, IF sampling

Most Recent Results

Keywords